Texas Instruments TMS320VC5510A 고정점 DSP

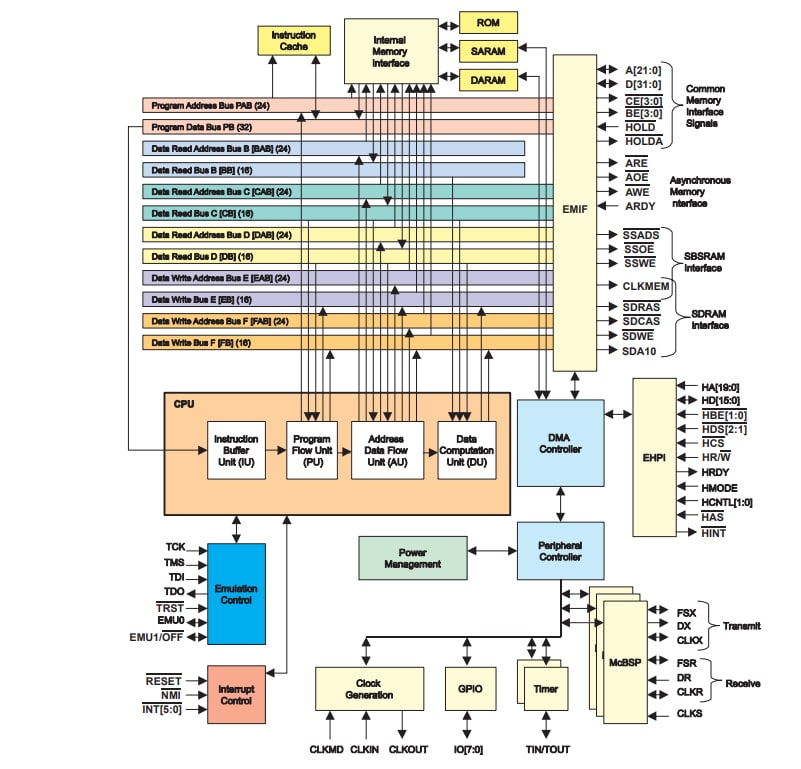

Texas Instruments TMS320VC5510A 고정점 디지털 신호 프로세서는 TMS320C55x DSP 세대 CPU 프로세서 코어에 기반을 두고 있습니다. 이 장치는 향상된 병렬 처리를 통해고 성능 및 저전력을 달성하고 전력 손실을 줄이는데 중점을 두는 C55x™DSP 아키텍처가 특징입니다. CPU는 프로그램 버스 1개, 데이터읽기 버스 3개, 데이터쓰기 버스 2개 및 주변기기 및 DMA 활동 전용 추가 버스를 포함하는 내부 버스 구조를 지원합니다. 이 버스는 단일 사이클에서 최대 3개의 데이터 읽기 및 2개의 데이터 쓰기를 수행할 수 있습니다. 병렬로, DMA 컨트롤러는 CPU 활동과 관계없이 사이클 당 최대 2개의 데이터 전송을 수행할 수 있습니다.TI TMS320VC5510A C55x CPU는 단일 사이클에서 17비트 x 17비트 곱셈이 가능한 2개의 MAC (곱셈-누적) 장치를 제공합니다. 추가 16비트 ALU는 중앙 40비트 ALU(산술/논리 장치)를 지원합니다. ALU를 사용하는 것은 명령 집합 제어 하에 있으므로 병렬 작동 및 소비전력을 최적화할 수 있습니다. 이러한 리소스는 C55x CPU의 AU(어드레스 장치) 및 DU(데이터 장치)에서 관리됩니다.

TMS320C55x DSP 코어는 애플리케이션별 하드웨어를 통해 특정 알고리즘에서 성능을 높일 수 있는 개방형 아키텍처로 제작되었습니다. TMS320VC5510A은 확장 기능을 통해 색 공간 변환, 사용자 인터페이스 작동, 보안, TCP/IP, 음성 인식 및 텍스트-음성 변환과 같은 추가 기능을 수행하기 위해 대역폭의 절반 이상으로 탁월한 비디오 코덱 성능을 제공할 수 있습니다.

특징

- 고성능, 저전력, 고정 소수점 TMS320C55x™ DSP(디지털 신호 프로세서)

- 명령 사이클 시간: 6.25/5ns

- 클록 속도: 160/200MHz

- 사이클당 1/2 개의 명령 실행

- 듀얼 멀티플라이어 최대 4억 MACS (초당 곱셈-누산)

- 산술/로직 장치 2개

- 내부 프로그램 버스 1개

- 3개의 내부 데이터/오퍼랜드 및 읽기 버스

- 2개의 내부 데이터/오퍼랜드 및 쓰기 버스

- 명령어 캐시(24 K 바이트)

- 다음으로 구성된 160 K x 16비트온칩 RAM

- 4 K × 16비트 DARAM (듀얼 액세스 RAM) (64 K 바이트) 로 구성된 블록 8개

- 4 K × 16비트 SARAM (단일 액세스 RAM) (256 K 바이트) 로 구성된 블록 32개

- 글루리스 인터페이스가 있는 32비트 EMIF (외부 메모리 인터페이스)

- 비동기 SRAM(정적 RAM)

- 비동기 EPROM

- SDRAM(동기식 DRAM)

- SBSRAM(동기식 버스트 SRAM)

- 16 K × 16비트 온칩 ROM (32 K 바이트)

- 8 M × 16비트 최대 주소 지정 가능 외부 메모리 공간

- 6개의 장치 기능 도메인의 프로그래밍 가능한 저전력 제어

- 온칩 주변 장치

- 20비트 타이머 2개

- 6채널 DMA (직접 메모리 액세스)컨트롤러

- McBSP(다중 채널 버퍼형 직렬 포트) 3개

- 16비트 병렬 EHPI (향상된 호스트 포트 인터페이스)

- 프로그래밍 가능한 DPLL(디지털 위상 잠금 루프) 클록 발생기

- GPIO(범용 I/O) 핀 8개 및 XF(전용 범용 출력)

- 온칩 스캔 기반 에뮬레이션 로직

- IEEE Std 1149.1 (jtag) 경계 스캔 로직

- 240단자 MicroStar BGA™, (볼 그리드 어레이) (GGW 접미사)

- 240단자 MicroStar BGA™, (볼 그리드 어레이) (ZGW 접미사) [무연]

- I/O 공급 전압: 3.3 V

- 코어 공급 전압: 1.6 V

애플리케이션

- 압축

- 비디오 처리

- 머신 비전

- 의료 영상 촬영

추가 리소스

블록 선도

게시일: 2020-10-14

| 갱신일: 2024-09-03