Texas Instruments TMS320VC5502 고정점 디지털 신호 프로세서

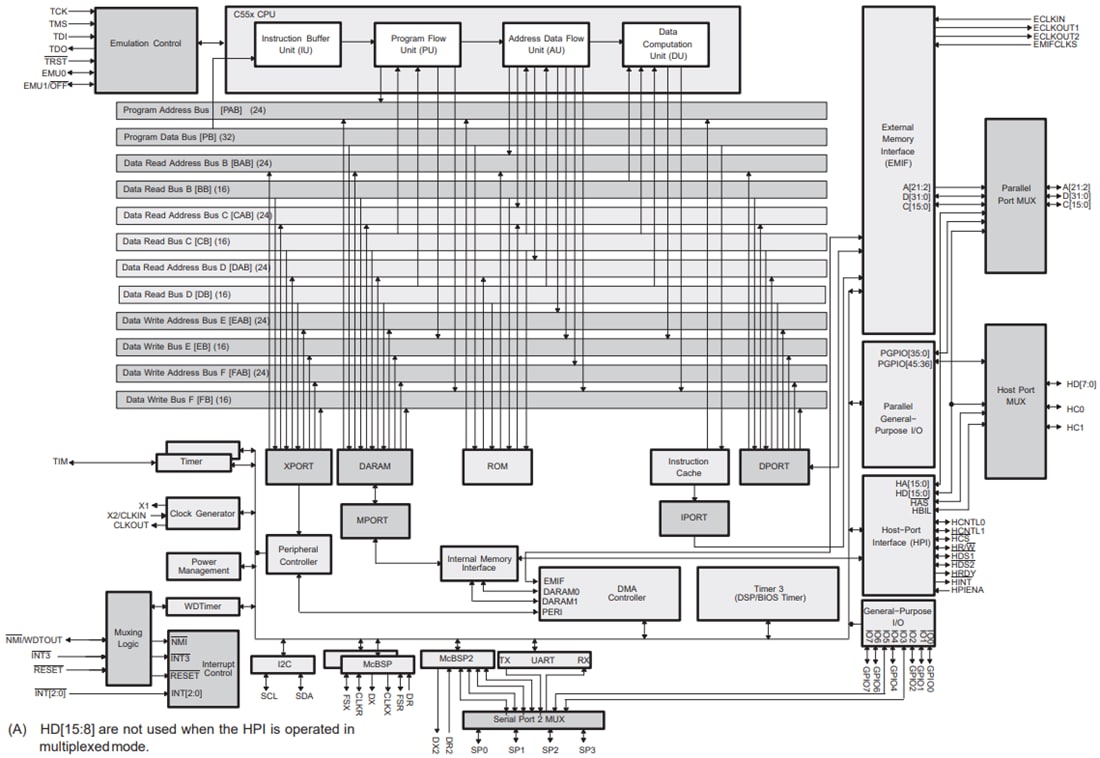

Texas Instruments TMS320VC5502 고정점 DSP(디지털 신호 프로세서)는 TMS320C55x DSP 세대 CPU 프로세서 코어에 기반을 두고 있습니다. Texas Instruments TMS320C55x DSP 아키텍처는 향상된 병렬화 및 전력 손실 감소에 중점을 두어 고성능 및 저전력을 달성합니다. CPU는 프로그램 버스 1개, 데이터 읽기 버스 3개, 데이터 쓰기 버스 2개, 주변장치 및 DMA 활동 전용 추가 버스로 구성된 내부 버스 구조를 지원합니다. 이 버스는 단일 사이클에서 최대 3개의 데이터 읽기와 2개의 데이터 쓰기를 수행할 수 있습니다. DMA 컨트롤러는 CPU 활동과 관계없이 병렬로 사이클당 최대 2개의 데이터 전송을 수행할 수 있습니다.TMS320C55x CPU는 단일 사이클에서 각각 17비트 x 17비트의 곱셈이 가능한 2개의 MAC(곱셈-누산) 장치를 제공합니다. 중앙 40비트 ALU(산술/로직 장치)는 추가 16비트 ALU에 의해 지원됩니다. ALU를 사용하는 것은 명령 집합 제어 하에 있으므로 병렬 작동 및 소비전력을 최적화할 수 있습니다. 이러한 리소스는 TMS320C55x CPU의 AU(어드레스 장치) 및 DU(데이터 장치)에서 관리됩니다. TMS320C55x DSP 세대는 향상된 코드 밀도를 위해 가변 바이트 폭 명령어 세트를 지원합니다. IU(지시 장치)는 내부 또는 외부 메모리에서 32비트 프로그램 페치를 수행하고 PU(프로그램 장치)에 대한 명령어를 대기열로 가져옵니다. 프로그램 장치는 명령을 해독하고 작업을 AU 및 DU 리소스로 전달하며 완전히 보호된 파이프 라인을 관리합니다. 예측 분기 기능은 조건부 명령 실행 시 파이프라인 플러시를 방지합니다.

TMS320C5502 주변 장치 세트에는 EPRAM 및 SRAM과 같은 비동기식 메모리뿐만 아니라 동기식 DRAM 및 동기식 버스트 RAM과 같은 고속 고밀도 메모리에 대한 글루리스 액세스를 제공하는 EMIF(외부 메모리 인터페이스)가 포함되어 있습니다. 추가적인 주변장치에 대한 예로 UART, 워치독 타이머 및 I-캐시를 들 수 있습니다. 3개의 전이중 McBSP(다중 채널 버퍼 직렬 포트)는 다양한 업계 표준 직렬 장치에 대한 글루리스 인터페이스와 최대 128개의 개별적으로 활성화된 채널과의 다중 채널 통신을 제공합니다. HPI(호스트 포트 인터페이스)는 5502의 내부 메모리 32 K 워드에 호스트 프로세서 액세스를 제공하는 데 사용되는 8/16비트 병렬 인터페이스입니다. HPI는 다양한 호스트 프로세서에 글루리스 인터페이스를 제공하기 위해 다중화 또는 비다중화 모드로 구성할 수 있습니다. DMA 컨트롤러는 CPU 개입 없이 6개의 독립적인 채널 컨텍스트에 대한 데이터 이동을 제공합니다. 2개의 범용 타이머, 8개의 전용 GPIO(범용 I/O) 핀 및 APLL(아날로그 위상 고정 루프) 클록 생성 장치도 포함되어 있습니다.

특징

- 고성능, 저전력, 고정 소수점 TMS320C55x™ DSP(디지털 신호 프로세서)

- 명령 사이클 시간: 3.33/5ns

- 클록 속도: 300/200MHz

- I-캐시(명령 캐시): 16Kbyte

- 사이클당 1~2개의 명령어가 실행됩니다.

- 듀얼 멀티플라이어[초당 최대 6억 곱셈-누적(MMACS)]

- 2개의 ALU(산술/로직 장치)

- 프로그램 버스 1개, 내부 데이터/피연산자 읽기 버스 3개, 내부 데이터/피연산자 쓰기 버스 2개

- 명령 캐시(16KB)

- 4K x 16비트 DARAM(Dual-Access RAM) 블록 8개로 구성된 32K x 16비트 온칩 RAM(64KB)

- 16K × 16비트 1 대기 상태 온 칩 ROM(32KB)

- 8M × 16비트 최대 어드레스 지정 가능 외부 메모리 공간

- GPIO(범용 입/출력) 기능과 글루리스 인터페이스로 EMIF(외부 메모리 인터페이스)를 지원하는 32비트 외부 병렬 버스 메모리

- 비동기 SRAM(정적 RAM)

- 비동기 EPROM

- SDRAM(동기식 DRAM)

- SBRAM(동기식 버스트 RAM)

- 에뮬레이션/디버그 추적 기능은 마지막 16개 PC(프로그램 카운터) 불연속성과 이전 32개 PC 값을 저장합니다.

- 6개의 장치 기능 도메인의 프로그래밍 가능한 저전력 제어

- 온칩 주변 장치

- 6채널 DMA(직접 메모리 액세스) 컨트롤러

- McBSP(다중 채널 버퍼형 직렬 포트) 3개

- 프로그래밍 가능한 APLL(아날로그 위상 잠금 루프) 클록 발생기

- GPIO(범용 I/O) 핀 및 전용 출력 핀(XF)

- 8/16비트 병렬 HPI(호스트 포트 인터페이스)

- 타이머 4개

- 64비트 범용 타이머 2개

- 64비트 프로그래밍 가능 워치독 타이머

- 64비트 DSP/BIOS™ 카운터

- I2C(내부 집적 회로) 인터페이스

- UART(범용 비동기 수신기/송신기)

- 온칩 스캔 기반 에뮬레이션 로직

- IEEE Std 1149.1(JTAG) 바운더리 스캔 로직

- 패키지

- 176 단자 LQFP(로우 프로파일 쿼드 플랫 팩) (PGF 접미사)

- 201 단자 MicroStar BGA™(볼 그리드 어레이) (GZZ 및 ZZZ 접미사)

- I/O 공급 전압: 3.3V

- 코어 공급 전압: 1.26V

기능 블록 선도