Texas Instruments AM654x/AM652x Arm™ 기반 프로세서

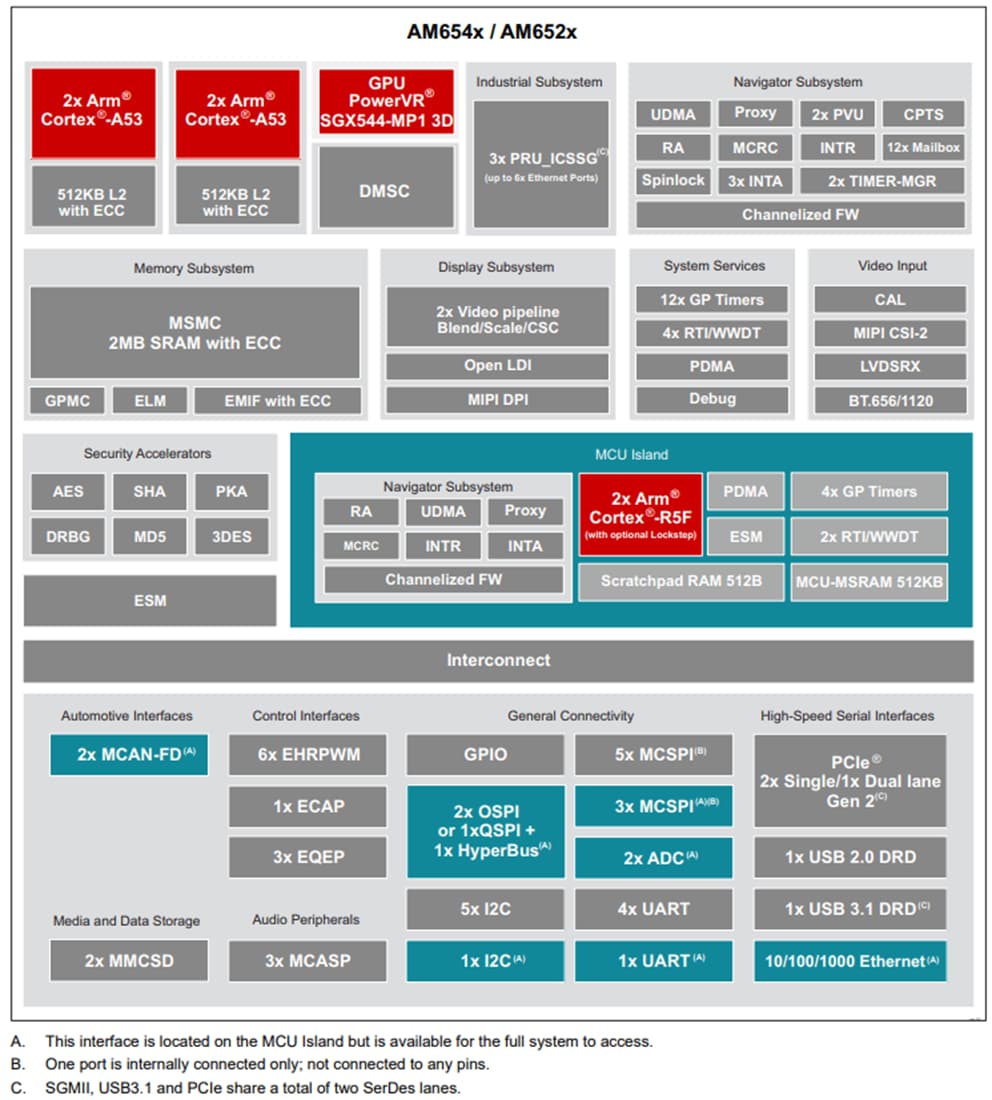

Texas Instruments AM654x/AM652x Arm™기반 프로세서는 최신 인더스트리 4.0 임베디드 제품의 복잡한 처리 요구 사항을 충족하도록 제작된 Arm® 애플리케이션 프로세서입니다. AM654x 및 AM652x 장치는 4개 또는 2개의 Arm® Cortex®-A53 코어를 듀얼 Arm Cortex-R5F MCU 서브 시스템과 결합합니다. 여기에는 고객이 최종 제품의 기능 안전 목표를 달성하는 데 도움이 되는 기능이 포함됩니다. 또한 기능 안전 애플리케이션을 위한 산업 연결 및 처리 기능을 갖춘 고성능 산업 제어가 가능한 SoC를 생성하기 위한 3개의 기가비트 산업 통신 서브 시스템(PRU_ICSSG)도 포함되어 있습니다. AM65xx는 현재 IEC 61508에 따라 TÜV SÜD 인증을 받기 위한 평가를 진행 중입니다.Cortex-A53에 있는 ARM AM654x 코어 4개는 공유 L2 메모리가 있는 듀얼 코어 클러스터 2개에 배열되어 처리 채널 2개를 생성합니다. AM652x에 있는 ARM Cortex-A53 코어 2개는 듀얼 코어 클러스터 1개와 단일 코어 클러스터 2개 옵션으로 제공됩니다. 광범위한 ECC가 신뢰성을 위한 칩 내장 메모리, 주변 기기, 상호 연결 장치에 포함되어 있습니다. SoC는 전체적으로 기능 안전 목표를 달성할 수 있는 고객 설계 시스템을 지원하기 위한 기능을 갖추고 있습니다. DMSC가 관리하는 세분화된 방화벽 외에 일부 AM654x 및 AM652x 장치에서 암호화 가속 및 보안 부팅 기능을 사용할 수 있습니다.

ARM Cortex-A53 RISC CPU는 ARM Neon™ 확장 기능으로 프로그래밍 가능성을 제공합니다. 듀얼 ARM Cortex-R5F MCU 서브 시스템은 2개의 코어로 일반적으로 사용하거나 기능 안전 애플리케이션의 요구사항을 충족시키기 위해 잠금 단계에서 사용할 수 있습니다. PRU_ICSSG 서브 시스템은 Profinet IRT, TSN, Ethernet/IP 또는 EtherCAT(많은 것들 중에서)와 같은 최대 6개의 산업용 이더넷 포트를 제공하거나 표준 기가비트 이더넷 연결에 사용할 수 있습니다.

Texas Instruments는 프로세서 SDK Linux, Linux-RT, RTOS, Android, C 컴파일러 및 소스코드 실행에 대한 가시성을 위한 디버깅 인터페이스를 포함한 ARM 코어를 위한 완전한 소프트웨어 및 개발 도구 세트를 제공합니다. 기능 안전 또는 보안 관련 시스템 개발 시 고객을 지원하기 위해 해당 기능 안전 및 보안 문서가 제공될 것입니다.

특징

- 프로세서 코어

- 최대 1.1GHz 듀얼 또는 쿼드 코어 ARM Cortex-A53 마이크로프로세서 서브시스템

- SECDED를 포함한 512KB L2 캐시가 있는 최대 2개 듀얼 코어 또는 2 개 싱글 코어 ARM Cortex-A53 클러스터

- 각 A53 코어에는 32KB L1 ICache 및 32K L1 DCache가 있음

- 최대 400MHz에서 듀얼 코어 ARM Cortex-R5F

- Lockstep 모드 지원

- R5F 코어당 16KB ICache, 16KB DCache 및 64KB RAM

- 최대 1.1GHz 듀얼 또는 쿼드 코어 ARM Cortex-A53 마이크로프로세서 서브시스템

- 산업 서브 시스템

- 3개의 기가비트 산업 통신 서브 시스템(PRU_ICSSG)

- PRU_ICSSG당 최대 10/100/1000 이더넷 포트 2개

- 2개의 SGMII 포트 지원

- 10/100Mb PRU-ICSS와의 호환성

- PRU_ICSSG당 24× PWM

- 사이클 단위 제어

- 향상된 트립 제어

- PRU_ICSSG당 18× 시그마-델타 필터

- 단락 로직

- 과전류 로직

- PRU_ICSSG당 6× 다중 프로토콜 위치 인코더 인터페이스

- 3개의 기가비트 산업 통신 서브 시스템(PRU_ICSSG)

- 메모리 서브 시스템

- 최대 2MB의 온칩 L3 RAM(SECDED 포함)

- MSMC(멀티코어 공유 메모리 컨트롤러)

- 최대 2MB(2 뱅크 × 1MB) SRAM(SECDED 포함)

- 공유 일관성 레벨 2 또는 레벨 3 메모리 매핑 SRAM

- 공유 일관성 레벨 3 캐시

- 256비트 프로세서 포트 버스 및 40비트 물리적 어드레스 버스

- 프로세서 또는 장치 마스터에 연결하기 위한 일관되고 통합된 양방향 인터페이스

- L2, L3 캐시 사전 예열 및 사후 플러싱

- 스타베이션 제한으로 대역폭 관리

- 인프라 마스터 인터페이스 1개

- 단일 외부 메모리 마스터 인터페이스

- 분산 가상 시스템 지원

- 내부 DMA 엔진 - DRU(데이터 라우팅 장치) 지원

- ECC 오류 보호

- 최대 2MB(2 뱅크 × 1MB) SRAM(SECDED 포함)

- DDR 서브 시스템(DDRSS)

- 최대 DDR-1600까지 DDR4 메모리 유형 지원

- 32비트 데이터 버스 및 7비트 SECDED 버스

- 8GB 주소 지정 가능 전체 공간

- GPMC(범용 메모리 컨트롤러)

- SafeTI™ 반도체 부품

- 기능 안전 애플리케이션을 위해 설계

- IEC 61508 요구사항에 따라 개발

- SIL-3의 체계적인 무결성 달성

- MCU 안전 아일랜드의 경우 SIL-2의 임의의 결함 무결성 요구사항을 달성하기 위한 충분한 진단 기능이 포함되어 있습니다.

- SoC의 나머지 부분에는 SIL-2의 임의의 결함 무결성 요구사항을 달성하기 위한 충분한 진단 기능이 포함되어 있습니다.

- 또한 적절한 안전 개념이 주어진 SIL-3 애플리케이션의 실행을 달성하기 위한 충분한 아키텍처 측정 지표가 마련되어 있습니다 (예: 소프트웨어로 상호 비교).

- 기능 안전 매뉴얼 제공

- 안전 관련 인증

- TÜV SÜD[인증 진행 중]에 의한 구성요소 레벨 기능 안전 인증

- 기능 안전 기능

- 계산 시 ECC 또는 패리티-중요한 메모리 및 내부 버스 인터커넥트

- FFI(Freedom From Interference) 제공에 도움이 되는 방화벽

- CPU, 하이엔드 타이머 및 칩 내장 RAM을 위한 BIST(자가 진단 테스트)

- 진단 테스트를 위한 하드웨어 오류 주입 지원

- 기능 안전 관련 오류를 캡처하기 위한 ESM(오류 신호처리 모듈)

- 전압, 온도 및 클록 모니터링

- 여러 클록 도메인의 창이 있는 및 창이 없는 워치독 타이머

- MCU 아일랜드

- 듀얼코어 ARM Cortex-R5F 마이크로프로세서 서브시스템 절연

- 별도의 전압, 클록, 리셋 및 전용 주변기기

- SoC 나머지 부분에 내부 MCSPI 연결

- 보안

- 안전한 부팅 지원

- 하드웨어 강화 신뢰 루트

- 백업 키를 통해 RoT(root-of-trust) 전환 지원

- 인수 보호, IP 보호, 롤백 방지 보호 지원

- 암호화 가속 지원

- 들어오는 데이터 스트림을 기반으로 키 재료를 자동 전환할 수 있는 세션 인식 암호화 엔진

- 암호화 코어 지원

- AES – 128/192/256비트 키 크기

- 3DES – 56/112/168비트 키 크기

- MD5, SHA1

- SHA2 – 224/256/384/512

- DRBG(순수 난수 생성기 포함)

- RSA/ECC 처리를 지원하는 PKA(공개 키 가속기)

- DMA 지원

- 디버깅 보안

- 보안 소프트웨어 제어 디버그 액세스

- 보안 인식 디버깅

- TEE(Trusted Execution Environment) 지원

- Arm TrustZone 기반 TEE

- 절연을 위한 광범위한 방화벽 지원

- 보안 DMA 경로 및 상호 연결

- 보안 워치독/타이머/IPC

- 보안 저장 지원

- OSPI 인터페이스를 위한 사용중 암호화 및 인증 지원

- 패킷 기반 하드웨어 암호화 엔진을 통한 데이터(페이로드) 암호화/인증을 위한 네트워킹 보안 지원

- 키 및 보안 관리용 DMSC(보안 보조 프로세서)(전용 장치 레벨, 보안 소프트웨어용 상호 연결 포함)

- 안전한 부팅 지원

- SoC 서비스

- DMSC(장치 관리 보안 컨트롤러)

- 중앙 집중식 SoC 시스템 컨트롤러

- 초기 부팅, 보안, 기능 안전 및 클록/리셋/전력 관리를 포함한 시스템 서비스 관리

- 액티브 및 저전력 모드용 전력 관리 컨트롤러

- 메시지 관리자를 통한 다양한 처리 장치와 통신

- 사용하지 않는 주변 장치를 최적화하기 위한 간소화된 인터페이스

- 추적 및 디버깅 기능

- 32비트 범용 타이머 16개

- 데이터 이동 및 제어 NAVSS(내비게이터 서브시스템) 2개

- 링 가속기(RA)

- UDMA(통합 DMA)

- TM(타이머 관리자) 최대 2개(각 1,024 타이머)

- DMSC(장치 관리 보안 컨트롤러)

- 멀티미디어

- 디스플레이 서브시스템

- 완전히 입력 매핑된 오버레이 관리자 2개, 디스플레이 출력 2개와 연결됨

- 포트 MIPI DPI 병렬 인터페이스 1개

- 포트 OLDI 1개

- PowerVR SGX544-MP1 3D GPU(그래픽 처리 장치)

- 카메라 직렬 인터페이스-2(MIPI CSI-2) 1개

- 포트 비디오 캡처 1개: BT.656/1120(임베디드 동기화 없음)

- 디스플레이 서브시스템

- 고속 인터페이스

- 기가비트 이더넷(CPSW) 인터페이스 지원 1개

- RMII(10/100) 또는 RGMII(10/100/1000)

- IEEE1588(2008 Annex D, Annex E, Annex F), 802.1AS PTP

- 오디오/비디오 브리징(P802.1Qav/D6.0)

- 에너지 효율 이더넷(802.3az)

- 점보 프레임(2,024바이트)

- Clause 45 MDIO PHY 관리

- PCIe(PCI-Express) revision 3.1 서브시스템 2 개

- Gen2(5.0GT/s) 작동 지원

- 독립 1-레인 또는 단일 2-레인 포트 2개

- 동시 루트-복합 및 엔드 포인트 작동 지원

- USB 3.1 DRD(Dual-Role Device) 서브시스템

- 향상된 SuperSpeed Gen1 포트 1개

- USB 2.0 포트 1개

- 각 포트는 USB 호스트, USB 주변기기 또는 USB DRD로 독립적으로 구성 가능

- 기가비트 이더넷(CPSW) 인터페이스 지원 1개

- 일반 연결성

- I2C™(상호 집적 회로) 포트 6개

- 구성 가능한 UART/IrDA/CIR 모듈 5개

- 다음으로 구성된 동시 플래시 인터페이스 2개

- OSPI 플래시 인터페이스 2개

- 또는 HyperBus™ 및 OSPI1 플래시 인터페이스

- 12비트 ADC(아날로그-디지털 변환기) 2개

- 최대 4M 샘플/초

- 다중 아날로그 입력 8개

- MCSPI(다중 채널 직렬 주변기기 인터페이스) 컨트롤러 8개

- 2개(내부 연결 포함)

- 6개(외부 인터페이스 포함)

- GPIO(범용 I/O) 핀

- 제어 인터페이스

- EHRPWM(Enhanced High-Resolution Pulse-Width Modulator) 모듈 6개

- ECAP(Enhanced Capture) 모듈 1개

- EQEP(Enhanced Quadrature Encoder Pulse) 모듈 3개

- 자동차 인터페이스

- CAN-FD 완전 지원이 되는 MCAN(모듈식 컨트롤러 영역 네트워크) 모듈 2개

- 오디오 인터페이스

- MCASP(다중 채널 오디오 직렬 포트) 모듈 3개

- 미디어 및 데이터 저장

- MMC™/SD(멀티미디어 Card™/보안 디지털) 인터페이스 2개

- 간소화된 전력 관리

- 이중 전압 I/O를 완벽하게 지원하는 간소화된 전원 시퀀스

- 통합 LDO로 전력 솔루션 복잡성 감소

- SD 인터페이스의 자동 전압 전환을 처리하기 위한 통합 SDIO LDO

- 통합 POR(파워 온 리셋) 생성으로 전력 솔루션 복잡성 감소

- 기능 안전 모니터링을 위한 통합 전압 감시 장치

- 빠른 전원 공급과도 전류 감지를 위한 통합 전원 공급 장치 글리치 감지기

- 아날로그/시스템 통합

- 통합 USB VBUS 감지

- DDR 재설정을 위한 오류 방지 I/O

- 버스 충돌을 방지하기 위해 재설정 중에 모든 I/O 핀 드라이버 비활성화

- 시스템 충돌을 방지하기 위해 재설정 중에 기본 I/O 완전 비활성화

- 동적 I/O pinmux 구성 변경 지원

- SoC(시스템 온 칩) 아키텍처

- UART, I2C, OSPI, HyperBus, 병렬 NOR 플래시, SD 또는 eMMC™, USB, PCIe 및 이더넷 인터페이스에서 1차 부팅 지원

- 28nm CMOS 기술

- 23mm × 23mm, 0.8mm 피치, 784핀 FCBGA(ACD)

애플리케이션

- 산업용 PLC(프로그래밍 가능 로직 컨트롤러)

- 공장 자동화(안전 기능 포함)

- 다중 프로토콜 필드버스 통신

- 산업용 PC

- 산업용 로봇

- HMI(휴먼 머신 인터페이스)

- 그리드 인프라 및 보호 계전기

- 로봇 모터 드라이브

비디오

기능 블록 선도