Renesas Electronics SLG47011 GreenPAK 프로그래밍 가능한 혼합 신호 매트릭스

Renesas Electronics SLG47011 GreenPAK 프로그래밍 가능한 혼합 신호 매트릭스는 일반적으로 사용되는 아날로그-디지털 변환과 혼합 신호 기능을 위한 소형, 저전력 솔루션을 제공합니다. 구성 가능한 로직과 함께 사용되는 유연한 데이터 수집 시스템은 최소한의 비용으로 다양한 기능을 구현할 수 있는 방법을 제공합니다. 사용자는 상호 연결 논리, 매크로셀, IO 핀을 구성하기 위해 OTP(원타임 프로그래밍 가능) NVM(비휘발성 메모리)를 프로그래밍하여 회로 설계를 생성 할 수 있습니다. Renesas SLG47011는 가전제품, 휴대용/휴대용 전자장비, 산업 자동화/제어, 개인용 컴퓨터/서버, PC 주변장치, 배터리 전압/전류 모니터링, 전력 모니터에 이상적입니다.특징

- SAR ADC(아날로그-디지털 컨버터)

- 4, 12, 10, 8비트 선택 가능 분해능

- 8비트 모드에서 최대 2.35Msps

- 최대 4개의 아날로그 채널 샘플링

- 병렬, I2C, SPI 출력 옵션

- 프로그래밍 가능한 이득 증폭기

- 1개~64개 이득 선택

- 차동, 단일 종단 모드

- 매스코어 - 증배기, 덧셈기, 뺄셈기, 변환기 옵션

- 독립적인 데이터 버퍼 4개

- 최대 8개의 16비트 워드 버퍼 길이

- 오버 샘플링 모드(ADC 분해능 증가)

- 이동 평균 모드

- 카운터 캡처 모드

- 4096 워드 x 12비트 메모리 테이블 매크로셀

- 전체 범위 모드 또는 2가지 범위 모드

- ADC 데이터 선형화 또는 Y = F(X) 기능

- ADR - 데이터/저장 모드

- 16비트 다중 채널 디지털 비교기(MDCMP)

- 최대 4개의 독립 채널 샘플링

- 정적 또는 동적 임계값

- 각 채널에 대한 히스테리시스 옵션

- PWM(펄스 폭 변조) 매크로셀

- 분해능: 12비트

- 동적 듀티 사이클 변경(최대 4096 듀티 사이클 값)

- 너비 컨버터 매크로셀

- 12비트 병렬 데이터 출력

- 옵션으로 제공되는 12 x 1비트, 6 x 2비트 또는 3 x 4비트 출력

- 12비트 333ksps DAC(디지털-아날로그 컨버터)

- 선택 가능한 전류원

- 통합 전압 레퍼런스(VREF)

- 구성 가능한 히스테리시스 및 레퍼런스가 있는 고속 아날로그 비교기

- 조합 기능 매크로셀 18개

- 2비트 LUT 또는 DFF/래치 매크로셀 2개

- 설정/리셋 기능이 있는 3비트 LUT 또는 DFF/래치 8개

- 선택 가능한 DFF/래치 또는 3비트 LUT 또는 시프트 레지스터 6개

- 4비트 LUT 또는 DFF/래치 2개(세트/리셋 매크로셀 포함)

- 다기능 매크로셀 14개

- 선택 가능한 DFF/래치 또는 3비트 LUT 10개+12비트 지연/카운터

- 선택 가능한 DFF/래치 또는 4비트 LUT+16비트 지연/카운터/FSM 2개

- 선택 가능한 DFF/래치 또는 3비트 LUT 1개+12비트 지연/카운터/FSM

- 12비트 메모리 제어 업/다운 카운터

- SPI 및 I2C 통신 인터페이스

- 에지 감지기 출력으로 프로그래밍 가능한 지연

- 디글리칭 필터 또는 에지 감지기

- 발진기(OSC) 2개

- 2kHz/10kHz 발진기

- 20MHz/40MHz 발진기

- 아날로그 온도 센서

- CRC를 사용한 POR(파워 온 리셋)

- 리드백 보호(읽기 잠금)

- 1.71 V ~ 3.6 V 전력 공급

- 작동 온도 범위: -40 °C~++85 °C

- 16핀 STQFN 패키지, 2.0mm x 2.0mm x 0.55mm, 0.4mm 피치

- 무할로겐 및 RoHS 준수

애플리케이션

- 가전제품

- 핸드헬드 및 휴대용 전자 제품

- 산업 자동화 및 공정 제어

- 개인용 컴퓨터 및 서버

- PC 주변 장치

- 배터리 전압 및 전류 모니터링

- 전력 모니터

데이터시트

- SLG47011-E - 아날로그-디지털 데이터 수집 시스템 및 확장된 온도 범위를 갖춘 GreenPAK 프로그래밍 가능한 혼합 신호 매트릭스

- SLG47011 – 아날로그-디지털 데이터 수집 시스템을 갖춘 GreenPAK 프로그래밍 가능한 혼합 신호 매트릭스

비디오

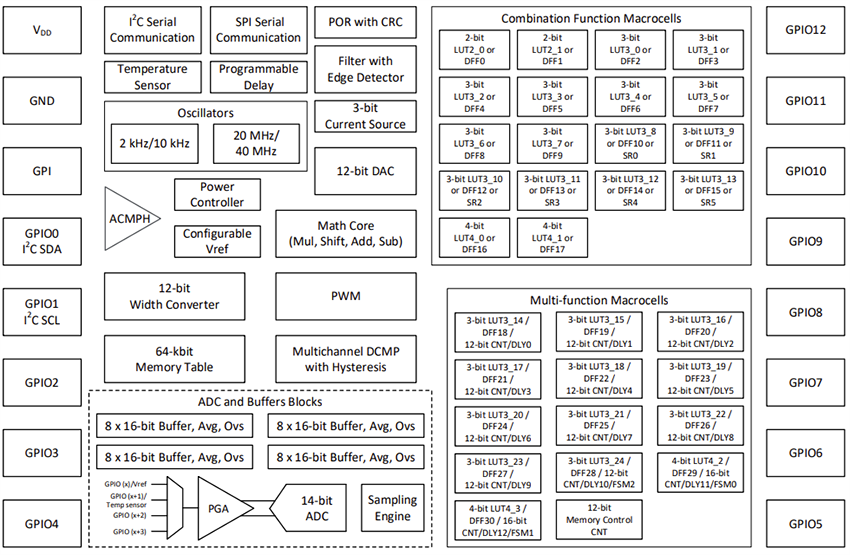

블록 선도

아날로그/디지털 블록 결합 구조

게시일: 2025-09-02

| 갱신일: 2025-12-30