Microchip Technology ZL3026x miClockSynth 범용 클록 생성기

Microchip ZL3026x miClockSynth 범용 클록 생성기는 여러 클록 주파수를 다중 부하에 분배하여 설계 신뢰성을 개선하고 BOM 비용을 줄이며 설계를 간소화합니다. ZL3026x 장치는 복잡한 클록 트리를 생성하여 보드 상의 여러 멀티플라이어, 합성기 및 발진기를 대체합니다. 소형 패키지와 동급 최고의 지터 성능을 갖춘 이 장치는 어려운 지터 예산과 보드 공간 제약이 있는 클록 합성 및 주파수 변환 애플리케이션을 대상으로 합니다.특징

- 유연한 입력 클록 4개

- 크리스털 /CMOS 입력 1개

- 차동/CMOS 입력 2개

- 단일 종단/CMOS 입력 1개

- 9.72MHz ~ 1.25GHz의 모든 입력 주파수(CMOS의 경우 최대 300MHz)

- 활동 모니터, 자동/수동 스위칭

- 핀 또는 레지스터로 글리치 없는 클록 스위칭

- 외부 또는 내부 EEPROM에서 전원을 켤 때 자동 자체 구성, 최대 8개 구성 핀 선택 가능

- 제로 지연 애플리케이션을 위한 외부 피드백

- 수치 제어식 발진기 모드

- 확산 스펙트럼 변조 모드

- PCIe 1, 2, 3 및 4 규격 준수 클록 생성

- 구성이 간편한 설계로 외부 VCXO 또는 루프 필터 구성 요소가 필요하지 않음

- SPI 또는 I2C 프로세서 인터페이스

- 코어 공급 전압 옵션

- 2.5V만 해당

- 3.3V만 해당

- 1.8V+2.5V

- 1.8V+3.3V

- 0.5mm 피치의 공간 절약형 8mm2 QFN-56

- 6x 또는 10x 모든 주파수, 모든 형식 출력

- 1Hz ~ 1045MHz의 모든 출력 주파수

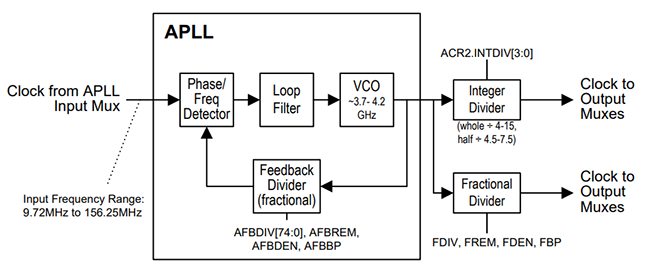

- 0ppm 오류의 고분해능 FRAC-N APLL(ZL30260-ZL30263)

- APLL에는 분수 분배기와 정수 분배기가 있어 2개의 독립적인 주파수 제품군 생성(ZL30260-ZL30263)

- 0ppm 오류의 분수형 N APLL 2개(ZL30264-ZL30267)

- 각 APLL에는 분수 분배기와 정수 분배기가 있어 총 4개의 독립 주파수 제품군 생성(ZL30264-ZL30267)

- 출력 지터

- 최저 0.17ps RMS(12kHz ~ 20MHz)의 정수 곱셈 및 분배기

- 분수 분배기에서 일반적으로 1ps RMS 미만, 0.5ps RMS 이하의 많은 주파수

- 각 출력에는 독립적인 분배기가 있음

- 각 출력은 LVDS, LVPECL, HCSL, 2xCMOS 또는 HSTL로 구성 가능

- 2xCMOS 모드에서 P 및 N 핀의 주파수가 다를 수 있음(예: 125MHz 및 25MHz)

- 1.5V ~ 3.3V의 CMOS 출력 전압을 제공하는 다중 출력 공급 전압 뱅크

- 정밀 출력 정렬 회로 및 출력 당 위상 조정

- 출력별 활성화/비활성화 및 글리치 없는 시작/정지(하이 또는 로우 정지)

애플리케이션

- 방송 영상

- 산업용 이더넷 네트워킹

- 데이터 센터

- 인포테인먼트

- HMI(휴먼 머신 인터페이스)

사양

- 공급 전압

- 2.375V~3.465V 더 높은 코어 범위

- 1.71V ~ 1.89V 낮은 코어 범위

- 1.71V ~ 2.625V 비클록 I/O 핀 범위

- 1.425V ~ 2.625V OCx 출력 범위

- 25MHz ~ 60MHz 크리스털 발진 주파수 범위

- 5pF 최대 션트 정전용량, 2pF(표준)

- 8pF ~ 16pF 부하 정전용량 범위, 10pF(표준)

- 50Ω -60Ω ESR(등가 직렬 저항) 범위

- 100µW, 200µW 및 300µW 최대 크리스털 구동 레벨(표준)

- 비클록 CMOS 핀

- ±10µA 입/출력 누설 전류

- 10pF 최대 입력 정전용량, 3pF(표준)

- 11pF 최대 입력 히스테리시스, 3pF(표준)

- GPIO 핀의 클록 출력

- 50MHz 주파수

- 표준 상승/하강 시간 범위: 1.2ns~2.3ns

- 40% ~ 60% XA 클록 입력 듀티 사이클 범위

- 클록 입력

- 0.1V ~ 1.4V 입력 차동 전압 범위

- 1.35VDC 표준 입력 바이어스 전압, 내부 바이어스

- 입력 주파수

- 9.72MHz~1250MHz 차동 범위

- 9.72MHz ~ 300MHz 단일 종단 범위

- 50kΩ 또는 80kΩ 표준 입력 저항

- LVDS 클록 출력

- 1045MHz 최대 주파수

- 공통 모드 전압 범위: 1.13V~1.37V

- 310mV ~ 530mV 차동 전압 범위

- 150ps(표준) 상승/하강 시간 범위

- 듀티 사이클 범위: 45%~55%

- LVPECL 클록 출력

- 1045MHz 최대 주파수

- 공통 모드 전압 범위

- VDDOx = 2.5V인 경우 1.13V ~ 1.33V

- VDDOx = 3.5V인 경우 1.85V ~ 2.05V

- 650mV ~ 1050mV 차동 전압 범위

- 150ps(표준) 상승/하강 시간 범위

- 듀티 사이클 범위: 45%~55%

- HCSL 클록 출력

- 250MHz 최대 주파수

- 공통 모드 전압 범위: 0.6V~0.95V

- 250ps(표준) 상승/하강 시간 범위

- 듀티 사이클 범위: 45%~55%

- CMOS 및 HSTL(클래스 I) 클록 출력

- 1Hz ~ 250MHz 최대 주파수 범위

- 0.4ns ~ 2.2ns 표준 상승/하강 시간 범위

- 듀티 사이클 범위: 42%~58%

- 출력 비활성화 시 표준 전류: 300µA

- APLL 주파수

- 3715MHz ~ 4180MHz VCO 범위

- 9.72MHz ~ 156.25MHz PFD 입력 범위

- 지터 및 스큐

- 600kHz(표준) APLL 지터 전송 대역폭

- 100ps(최대) 출력 간 스큐

- -40°C~++85°C 작동 온도 범위

APLL 블록 선도

추가 자료

게시일: 2023-08-18

| 갱신일: 2023-08-22