Infineon Technologies S70KL1282 및 S70KL1283 인터페이스 HyperRAM

Infineon Technologies S70KL1282 및 S70KL1283 인터페이스 HyperRAM은 HYPERBUS™ 인터페이스가 있는 고속 CMOS, 자동 새로고침 DRAM입니다. DRAM 어레이는 주기적으로 새로고침이 필요한 동적 셀을 사용합니다. 메모리가 HYPERBUS 인터페이스 마스터(호스트)에 의해 능동적으로 읽히거나 기록되지 않을 때 장치 내의 새로고침 제어 로직이 DRAM 어레이의 새로고침 작업을 관리합니다. 호스트가 새로고침 작업을 관리할 필요가 없으므로 DRAM 어레이는 마치 메모리가 새로고침 없이 데이터를 유지하는 정적 셀을 사용하는 것처럼 호스트에 나타납니다. 이 메모리는 정확하게 말하면 PSRAM(Pseudo-Static RAM)입니다.특징

- 인터페이스

- HYPERBUS 인터페이스

- 1.8V/3.0V 인터페이스 지원

- 단일 종단 클록(CK) - 버스 신호 11개

- 선택적 차동 클록(CK, CK#) - 버스 신호 12개

- 칩 선택(CS#)

- 8비트 데이터 버스(DQ[7:0])

- 하드웨어 리셋(RESET#)

- 양방향 RWDS(읽기-쓰기 데이터 스트로브)

- 새로고침 레이턴시 표시를 위해 모든 트랜잭션 시작 시 출력

- 읽기 트랜잭션 중 RDS(Read Data Strobe)로 출력

- 쓰기 트랜잭션 중 WDM(Write Data Mask)으로 입력

- 옵션 DCAR(DDR 중앙 정렬 읽기 스트로브)

- 읽기 트랜잭션 중 RWDS는 CK로부터 위상 변환된 두 번째 클록에 의해 오프셋됨

- 위상 변환 클록은 판독 데이터 아이 내에서 RWDS 전환 에지를 이동하는데 사용됩니다.

- 성능, 전력 및 패키지

-

- 200MHz 최대 클록 속도

- DDR - 클록의 양쪽 엣지에서 데이터를 전송합니다.

- 최대 400MBps(3,200Mbps)의 데이터 처리량

- 구성 가능한 버스트 특성

- 선형 버스트

- 래핑된 버스트 길이

- 16바이트(8클록)

- 32바이트(16클록)

- 64바이트(32클록)

- 128바이트(64클록)

- 하이브리드 옵션 - 64Mb에서 버스트 다음에 오는 하나의 래핑된 선형 버스트 다이 경계를 넘는 선형 버스트는 지원되지 않습니다.

- 출력 구동 강도 설정 가능

- 전력 모드

- 하이브리드 절전 모드

- 딥 파워 다운

- 어레이 새로고침

- 부분적 메모리 배열(1/8, 1/4, 1/2 등)

- 전체

- 패키지

- 24볼 FBGA

-

- 산업용(I): –40~+85°C

- 산업용 플러스(V): -40~+105°C

- 자동차용, AEC-Q100 등급 3 –40~+85°C 작동 온도 범위

- 자동차용, AEC-Q100 등급 2: –40~+105°C

- 구성 가능한 버스트 특성

-

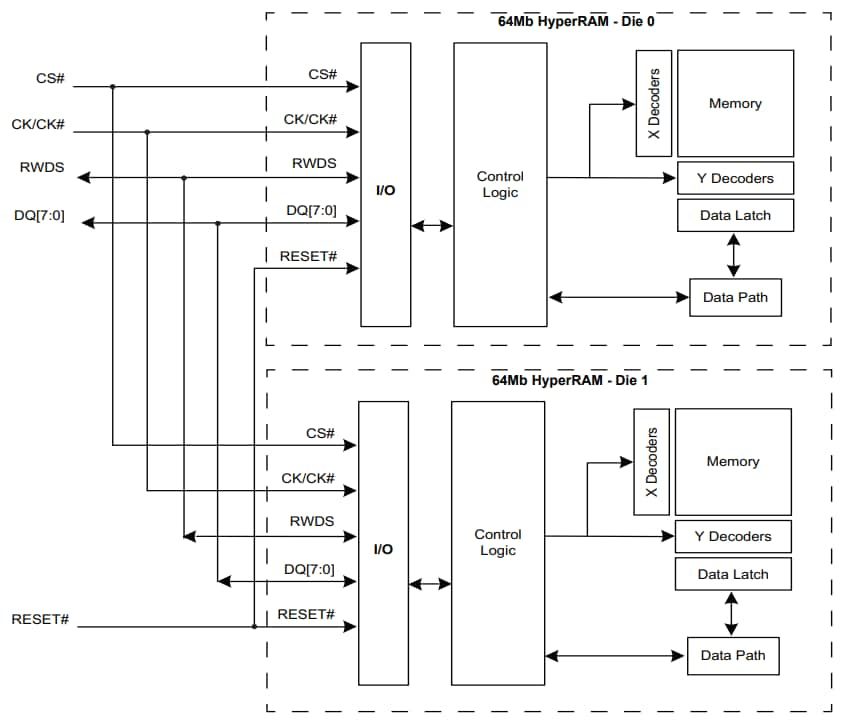

블록 선도

게시일: 2021-05-11

| 갱신일: 2023-09-04