Altera Stratix® 10 FPGA 및 SoC FPGA

Altera Stratix® 10 FPGA 및 SoC FPGA는 성능, 전력 효율, 밀도 및 시스템 통합을 상당히 개선합니다. Altera Stratix 10은 내장형 EMIB(다중 다이 상호 연결 브리지), AIB(고급 인터페이스 버스) 및 ChipLET와 같은 기술을 결합한 Altera의 혁신적인 SuperFPGA 아키텍처 ™를 활용합니다. 결과적으로 Altera Stratix 10 장치는 이전 세대 고성능 FPGA에 비해 최대 2배 더나은 성능을 달성할 수 있습니다.고처리량 시스템의 고성능 요구사항에 부응하

도록 설계된 Altera Stratix 10 GX FPGA입니다.

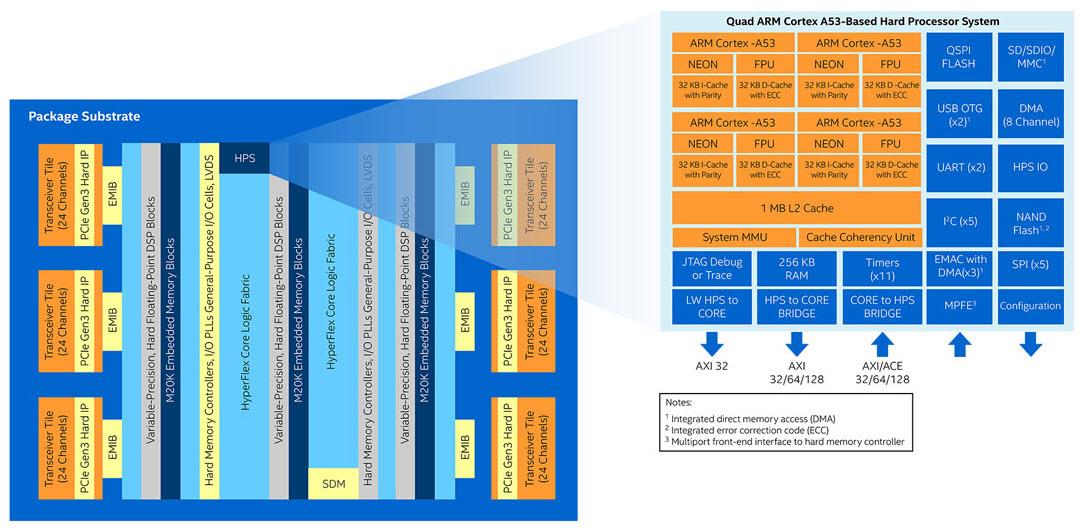

Altera Stratix 10 SX SoC FPGA

는 64비트 쿼드 코어 Arm® Cortex-A53 프로세서가 있는 하드 프로세서 시스템이 특징입니다.

Altera Stratix 10 TX FPGA는 H- 및 E- 송수신기 타일을 결합하여

업계에서 가장 진보된 송수신기 기능을 제공합니다.

HPC(고성능

컴퓨팅)을 위한 Altera Stratix 10 MX FPGA 필수 다기능 가속기입니다.

Altera Stratix 10 DX FPGA는 향후 선택된

Altera Xeon 확장 가능 프로세서에 직접 일관성 있는 연결을 위해 Altera Ultra Path 상호연결을 지원합니다.

고처리량 시스템의 고성능 요구 사항을 충족하

도록설계된 Altera Stratix 10 NX FPGA입니다.

Altera Stratix 10 AX FPGA는 고성능 데이터 컨버터를 통합하여

직접 RF 기능을 제공합니다.

특징

- 2배의 코어 클록 주파수 성능을 활용하여 처리량 대폭 증대

- Altera Hyperflex FPGA 아키텍처로 구현된 감소된 IP 크기를 사용하여 여러 장치를 단일 장치에 통합하여 이전 세대 장치 대비 최대 70%까지 전력을 줄임

- 버스 폭을 줄이고 IP(지적 재산) 크기를 줄이기 위한 더 빠른 클록 주파수로 추가 FPGA 리소스를 확보하여 더 큰 기능을 추가할 수 있음

- Hyper-Aware 설계 도구를 사용하여 라우팅 혼잡을 줄이고 설계 반복을 줄여 성능 향상

애플리케이션

- 모놀리식 FPGA 패브릭을 사용하여 설계 분할 복잡성을 줄임으로써 더 높은 생산성을 위한 ASIC 시제품화

- 900MHz를 통한 사이버 fMAX 보안을 통해 라인 속도로 지원되는 모든 프로토콜을 모니터링할 수 있음

- 획기적인 계산 처리량을 실현하기 위한 향후 Altera Xeon 확장 가능 프로세서 및 Altera Hyperflex FPGA 아키텍처 탑재 PCIe Gen4 x16, 구성 가능 DSP 엔진, AI 테스터 블록과의 직접적 일관적 연결을 위한 UPI를 통한 데이터 센터 가속화

- Altera Hyperflex FPGA 아키텍처를 사용하여 700 MHz을 통한 fMAX, 400 G 이더넷 지원

- IEEE 754-준수 단일 정밀 부동 소수점 성능이 최대 8.6TFLOPS인 레이더가 작은 전력으로 GPU 등급 성능을 제공

- 57.8 Gbps 및 28.9 Gbps 경로로 30G 백플레인 지원을 제공하는 송수신기 타일의 이종 3D SiP(System-in-Package) 통합을 포함한 OTN/데이터 센터 상호연결장치

사양

- 쿼드 코어 ARM Cortex-A53 MPCore 프로세서 클러스터 최대 1.5GHz

- VFPU(벡터 부동 소수점 장치) 단일 및 이중 정밀도, 각 프로세서용 ARM Neon 미디어 처리 엔진

- 패리티가 있는 32KB L1 명령 캐시, ECC(오류 수정 코드)가 있는 32KB L1 데이터 캐시

- 1MB KB 공유 L2 캐시(ECC 포함)

- 256KB 온 칩 RAM

- 시스템 메모리 관리 장치는 통합 메모리 모델을 구현하고 하드웨어 가상화를 FPGA 패브릭에 구현한 주변기기로 확장합니다.

- 캐시 일관성 장치는 CCU 마스터가 ARM Cortex-A53 MPCore CPU의 일관성 메모리를 볼 수 있도록 허용하는 원웨이(I/O) 일관성 장치를 제공합니다.

- 8 채널 DMA(직접 메모리 액세스)

- DMA가 통합된 10/100/1000 EMAC 3개

- USB OTG 2개(통합 DMA 포함)

- 16550 호환 UART 2개

- SPI(직렬 주변기기 인터페이스)컨트롤러 4개

- I2C 5개

- eMMC 4.5 1개(DMA 및 CE -ATA 포함), SD/SDIO/MMC 컨트롤러 지원

- ONFI 1.0 이상의 8 및 16비트 지원 NAND 플래시 컨트롤러 1개

- 최대 48개 소프트웨어 프로그래밍 가능 GPIO

- 범용 타이머 4개, 워치독 타이머 4개

- 시스템 관리자는 시스템 레벨 기능 및 기타 HPS 모듈을 제어하기 위한 메모리 매핑 제어 및 상태 레지스터와 논리를 포함합니다.

- Reset 관리자는 HPS 및 FPGA 패브릭의 소스의 재설정 요청과 모듈 리셋 제어 레지스터에 대한 소프트웨어 쓰기를 기반으로 신호를 재설정합니다.

- 클록 관리자는 HPS에서 생성된 모든 클록을 구성하기 위해 소프트웨어 프로그래밍 가능 클록 제어 기능을 제공합니다.

SoC FPGA 블록 선도

비디오

게시일: 2023-09-25

| 갱신일: 2026-01-07