Analog Devices Inc. SHARC® 프로세서

Analog Devices SHARC® 프로세서는 탁월한 코어 및 메모리 성능, 뛰어난 I/O 쓰루풋으로 부동 소숫점 DSP 시장을 평정하였습니다. 이 프로세서는 Super Harvard 아키텍처를 기반으로 하므로 탁월한 코어 및 메모리 성능과 뛰어난 뛰어난 I/O 쓰루풋 능력을 제공합니다. SHARC 프로세서는 대형 메모리 어레이와 애플리케이션별 주변 장치를 통합하여 제품 개발을 단순화하고 및 출시 시간을 단축합니다. 이 프로세서는 자동차, 공정 제어, 모터 제어 애플리케이션에 사용됩니다.특징

- 32/40비트 IEEE 부동 소숫점 수학

- 64비트 제품 및 80비트 누적의 32비트 고정 소숫점 배수기

- 산술 파이프라인 없음

- 하드웨어 내 6단 중첩 제로 오버헤드 루프 연산

- 풍부한 대수 연산 어셈블리어 구문

- 조건부 연산, 비트 연산, 나누기 및 제곱근, 비트 필드 저장 및 추출을 지원하는 명령 세트

- DMA를 통해 프로세서 개입 없이 풀 클럭 속도로 제로 오버헤드 백그라운드 전송 가능

애플리케이션

- 자동차 관련 산업

- 모터 및 전력 제어

- 공정 제어

- 보안 및 감시

- 테스트 및 측정

비디오

특징

- SHARC+ 코어당 최대 450MHz

- 패리티 포함 코어당 최대 3Mb L1 SRAM 메모리(캐시 용도로 구성할 수 있는 옵션 기능 제공)

- 32비트, 40비트 및 64비트 부동 소숫점 연산 지원

- 32비트 고정 지원

- 강력한 DMA 시스템

- 온칩 메모리 보호

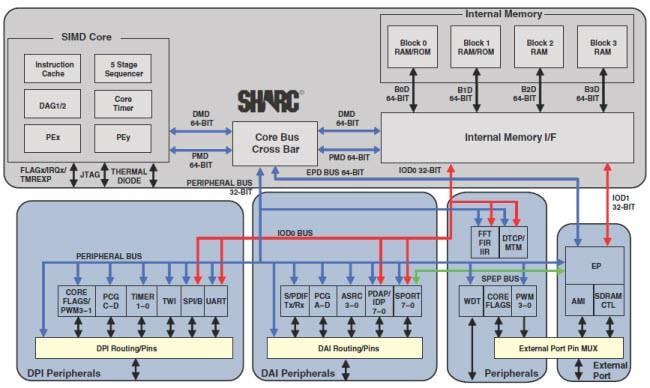

기능 블록 선도

Planning For Success In Real-Time Audio Processing

A standalone audio DSP optimized for low latency processing is likely to lead to increased robustness, decreased development time, and optimal scalability to accommodate future system needs and performance tiers.

게시일: 2013-05-23

| 갱신일: 2025-10-01